According to reports, Japanese semiconductor manufacturer Rapidus and multinational company IBM have announced a joint development partnership aimed at establishing mass production technology for chip packaging. The agreement builds on the existing collaboration between the two companies to jointly develop 2nm node technology, through which Rapidus will acquire high-performance semiconductor packaging technology from IBM, and the two companies will collaborate with the goal of further innovating this area.

The agreement is part of an international collaboration within the framework of the "Development of Design and Manufacturing Technology for 2nm Semiconductor Chips and Packages" project being carried out by the New Energy and Industrial Technology Development Organization (NEDO) in Japan and builds on an existing agreement with IBM for joint development of 2nm node technology. As part of the agreement, IBM and Rapidus engineers will collaborate on the development and manufacture of semiconductor packages for high-performance computer systems at IBM's North American facility.

IBM has accumulated R&D and manufacturing know-how for semiconductor packaging for high-performance computer systems over the years. The company also has extensive experience in joint development partnerships with Japanese semiconductor manufacturers and manufacturers of semiconductors, packaging manufacturing equipment and materials. Rapidus aims to leverage this expertise to quickly build cutting-edge chiplet packaging technology.

A 2nm chip refers to the node size in the chip manufacturing process and is used to represent the size of the transistors and other components on the chip. Adopting a smaller node size can help improve the performance and power efficiency of the chip. Specifically, 2nm node technology means that transistors and other electronic components can be sized up to 2nm during the chip manufacturing process, which allows more transistors to be accommodated in the same size chip area, increasing integration and processing power.

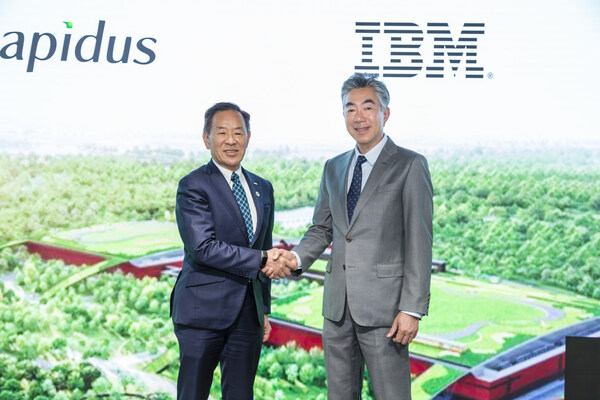

Pictured: Rapidus and IBM expand collaboration to develop second-generation semiconductor chip packaging technology

Since 2nm node technology allows more transistors to be placed in a smaller space, it can significantly increase the level of chip integration. This allows the chip to process more data and has more computing power.

Higher integration means that more transistors can work in parallel, improving the performance of the chip. In addition, the smaller transistor size also means a shorter current path and lower resistance, further increasing the speed at which the chip can operate.

Since 2nm node technology allows more transistors to be placed in a smaller space, it can reduce power loss in the circuit. In addition, the adoption of new technologies, such as back-side power supply, can further reduce power consumption and improve the energy efficiency ratio of chips.

Dr. Atsuyoshi Koike, President and CEO of Rapidus, commented, "Building on our current joint development agreement for 2nm semiconductor technology, we are very pleased to officially announce today our collaboration with IBM to build chip packaging technology. We will make full use of this international cooperation and take steps to enable Japan to play a more important role in the semiconductor packaging supply chain. ”

"IBM is proud to expand our collaboration with Rapidus to develop state-of-the-art chiplet technology based on decades of innovation in advanced packaging," said Darío Gil, senior vice president and research director at IBM. Through our agreements, we are committed to supporting the development of state-of-the-art node production processes, designs, and packages, as well as developing new use cases and supporting the semiconductor workforce. ”